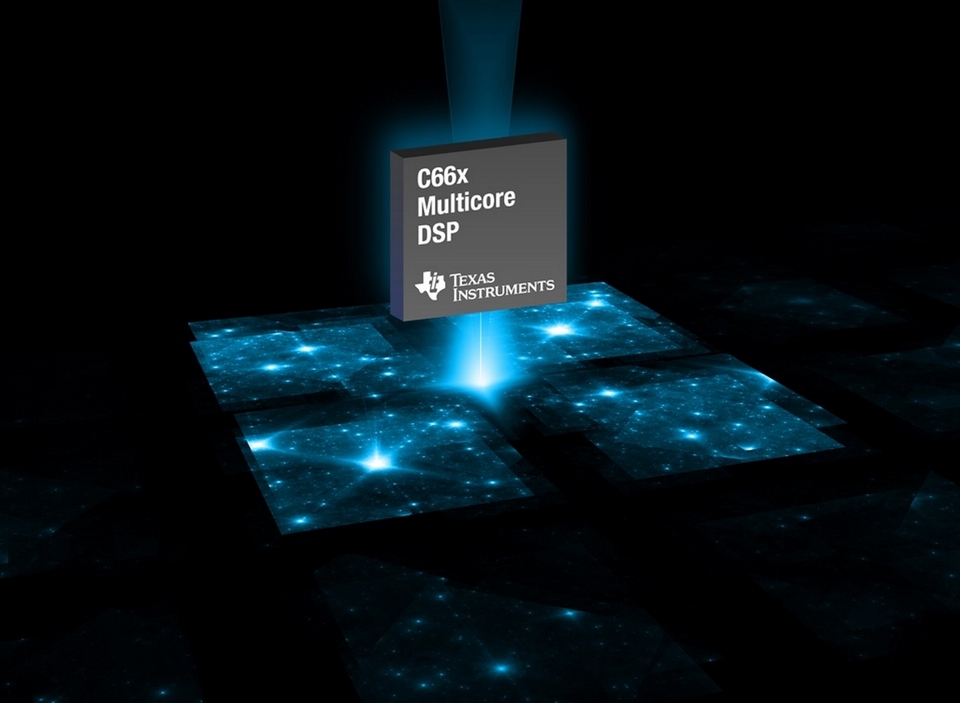

Ti a récemment dévoilé sa nouvelle gamme de processeurs SoC KeyStone II, spécifiquement conçus pour le calcul intensif. Cette gamme compte six composants, tous architecturés autour d’un processeur ARM TMS320C66x (alias C66x) de type Cortex A15 CoreMP. L’originalité vient de l’adjonction au CPU d’un ou plusieurs DSP (Digital Signal Processor), spécialité de longue date du fondeur américain.

La capacité de calcul de chacun des six composants varie ainsi selon le nombre de CPU (1, 2 ou 4) et de DSP (jusqu’à 8). Chaque groupe de cœurs (CPU et DSP) dispose d’une mémoire cache partagée, épaulée par 4 Mo de cache L3. La conception de Keystone II est tournée vers les traitements massivement parallèles, avec un accent tout particulier mis sur la communication inter-cœurs ARM-ARM, ARM-DSP et DSP-DSP. Celle-ci s’effectue au travers d’une liaison interne à haut débit baptisée TeraNet, conjuguée à un répartiteur d’instructions nommé MultiCore Navigator. La communication entre multiples SOC est quant à elle assurée par une connexion très basse latence HyperLink à relativement haut débit (50 Gbps)

Curieusement, la gamme KeyStone est presque née par accident : c’est en mettant au point les DSP pour la téléphonie 4G et en leur ajoutant des capacités de calcul en virgule flottante que les ingénieurs texans se sont retrouvés avec des composants dotés d’un rapport puissance/consommation parmi les meilleurs actuellement. Ainsi, une carte contenant 4 composants octo-DSP cadencés à 1 GHz ne consomme que 50 watts pour une puissance de calcul de 512 Gflops en simple précision ou 192 Gflops en double précision.

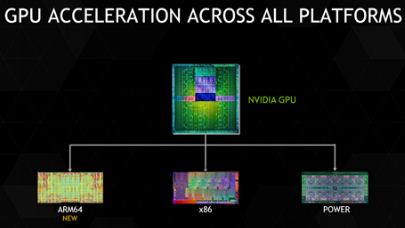

Cette approche CPU+DSP se différencie de l’approche GP-GPU pure. Les performances sont encore légèrement en retrait en termes de fréquence, mais elles se révèlent supérieures en termes d’efficacité énergétique, avec un ratio remarquable de 16 Gflops SP par Watt. Rappelons également que, concernant l’offre à base de Xeon, les spécifications sont de 1331 Gflops pour une consommation de 225 Watts, soit une performance énergétique de 6 Gflops/W.

Texas Instruments estime que le gain se traduit aussi en termes de parallélisation des applications, les développeurs maîtrisant l’architecture ARM n’ayant alors plus qu’à décharger les portions de code qui s’y prêtent sur les DSP. Plus facile à dire qu’à faire, mais pour cela le fondeur propose son propre IDE sur base Eclipse, Code Composer Studio (http://www.ti.com/tool/ccstudio). Les activités hautes performances visés par Ti sont les débits réseau (commutation de paquets et Ethernet switching), la sécurité (algorithmes de cryptage) et les métierss ayant à manipuler des signaux : imagerie médicale ou militaire, applications radar et multimédia (décodage et traitements vidéo), notamment.

Plus d’infos : www.ti.com/multicore

© HPC Today 2024 - All rights reserved.

Thank you for reading HPC Today.