L’édition 2013 de l’Intel Developer Forum qui s’est tenue à San Francisco voici quelques jours a montré une fois encore combien l’industrie du processeur était en train de se réinventer. En cause bien sûr, la chute ininterrompue des ventes d’ordinateurs personnels, qui contraint les fondeurs à multiplier les annonces autour des SoC pour appareils mobiles et des puces à très faible consommation. Les cartes sont-elles en cours de redistribution ? Tandis qu’AMD mise sur une gamme étoffée de processeurs embarqués, Intel se mobilise tous azimuts pour maintenir son chiffre d’affaires dans l’ère Post-PC qui se profile. Et le fait savoir.

Ainsi, parmi les attractions les plus marquantes cette année, on comptait un PC portable motorisé par un SoC Broadwell en 14 nm, un smartphone animé par un Atom Silvermont en 22 nm et Quark, une nouvelle famille de processeurs x86 dont le volume est 5 fois inférieur à l’Atom et la consommation divisée par 10. A priori, cette gamme se destine aux objets et aux vêtements intelligents (“wearable computing”). Mais la grande nouveauté est que Quark est une architecture ouverte, extensible par blocs pouvant provenir d’architectes tiers et que, par la même occasion, ces chaînes pourront être louées pour des projets non-Intel.

Si Quark reprend à son compte une certain nombre des spécificités industrielles qui ont fait le succès d’ARM, à l’autre extrémité du spectre, Intel domine toujours largement son sujet. Le haut de gamme Xeon E5-2600 va ainsi connaître une dernière mise à jour avant l’arrivée de la nouvelle génération.

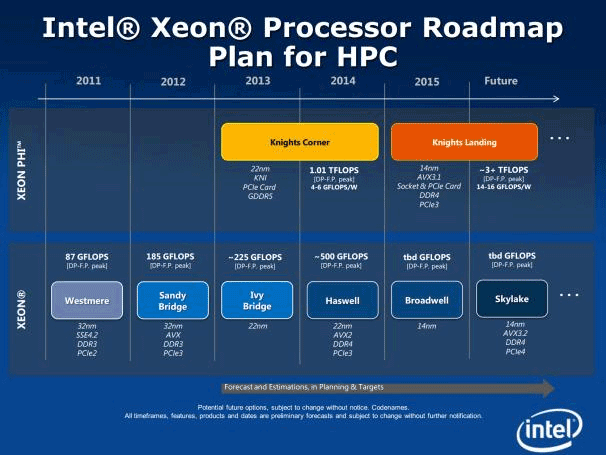

Cet update n’a rien d’une surprise, ses spécifications ayant fuité depuis plus d’un an : gravée en 22 nm, Xeon E5 2600 v2 se caractérise par une puissance accrue de 50 % et une efficacité énergétique améliorée de 45 %. Pour cela, le nombre maximum de cœurs passe à 12 (soit 24 threads exécutables en simultané), la mémoire cache à 30 Mo et la cadence des échanges mémoire passe à 1866 MHz (contre 1600). Sur son site Web, Intel annonce 536 Gflops au LINpack Matrix Multiplication, une performance remarquable si elle est avérée. En effet, on ne s’attendait pas à ce que Xeon passe la barre des 500 Gflops avant l’année prochaine et le lancement de l’architecture Haswell. Il faudra toutefois attendre cette dernière pour voir Xeon supporter la mémoire DDR4 et bénéficier du nouveau jeu d’instructions vectorielles AVX2, déjà surnommé “Haswell New Instructions”. On évoque déjà 14 cœurs et 35 Mo de cache. Rendez-vous en 2014 pour la confirmation.

Comme chaque année, septembre a également été pour Intel l’occasion de mettre à jour ses deux outils de développement intégrés, Cluster Studio et Parallel Studio. Au menu, le support de OpenMP 4.0, une intégration plus fluide des ressources de programmation communes à Xeon et Xeon Phi et de grosses améliorations sur le support de Fortran 2003 et 2008. James Reinders, porte-parole d’Intel Software & Tools Group, voit d’ailleurs en ce dernier, pour peu qu’il soit utilisé avec OpenMP 4.0, “le meilleur langage de programmation scientifique pour les architectures à haute performance“. Nos lecteurs les plus assidus ne seront pas étonnés de lire qu’on y reviendra en détails très très bientôt…

© HPC Today 2024 - All rights reserved.

Thank you for reading HPC Today.